المعالجات الحديثة معقدة

إن كنت قد درست مقرر معمارية الحاسوب Computer Architecture كما درسته أنا، مؤكد أنك مررت بتقسيم المعالجات إلى نوعين منفصلين ذو تعليمات مركبة CISC و ذو تعليمات مختزلة RISC. بدأ التقسيم بداية الثمانينات حين قدم مجموعة من أساتذة حامعة بيركيلي ورقة بعنوان The case for Reduced Instruction Set Computer، حيث بدأ تقسيم المعالجات حينها إلى نوعين متضادين، الأول ينفذ تعليمات كثيرة و مركبة Complex، ذات أطوال متغيرة variable-length encoding، تأخذ دورات زمنية متعددة many clock cycles، تعمل التعليمات على الذاكرة و المسجلات register-memory، هذه التعليمات مخزنة في برنامج microcode في ذاكرة مقروءة ROM و لها عدد أصغر من المسجلات. الثاني ينفذ تعليمات قليلة و بسيطة Reduced، ذات أطوال ثابتة fixed-length encoding، تعمل على المسجلات فقط register-register البيانات من الذاكرة لها تعليمات خاصة تحميل و تخزين load-store، مصممة بأن كل تعليمة لها دورة زمنية واحدة one clock per instruction، و هذه التعليمات ثابتة التوصيلات hardwired و لها عدد أكبر من المسجلات.

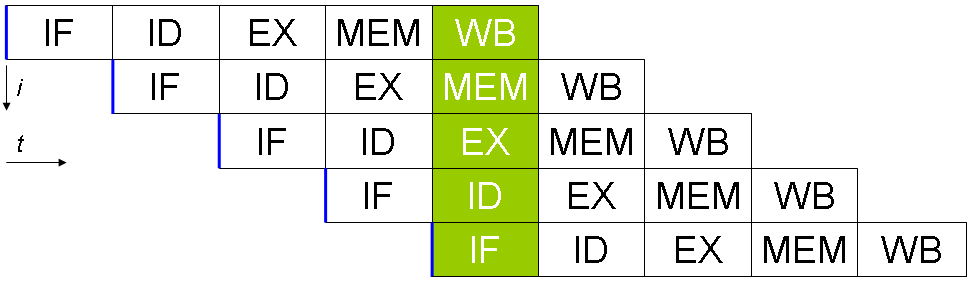

ينجز المعالج التعليمات البرمجية خلال دورة جلب-تحليل-تنفيذ fetch-decode-execute. في البداية يجلب المعالج التعليمة من الذاكرة، ثم يحللها و يعرف ما تفعله، ثم ينفذها و يخزن النتائج. أتت مفاهيم RISC لصناعة معالجات طبيعة التعليمات البسيطة فيها و التي ينفذها المعالج خلال دورة زمنية واحدة يسهل تنسيقها في خطوط متوازية pipelining للاستفادة أكثر من دورات المعالج. في الخطوط المتوازية، تنفذ المراحل بدرجة من التوازي. في أي تعليمة، يبدأ المعالج بجلب التعليمة من الذاكرة، ثم يحلل هذه التعليمة، أثناء تحليلها، يجلب المعالج التعليمة التي تليها، بعد ذلك ينفذ التعليمة الأولى، و يحلل التعليمة الثانية،و هكذا يستمر عمله. مواصفات RISC تسهل ذلك على عكس CISC.

pipelining

منذ ذلك الحين و كتب معمارية الحاسوب تصنف المعالجات إلى هذين التصنيفين. لمن لم يدرس هذا المقرر، يعد مقرر معمارية الحاسوب من أصعب المقررات التي يمر بها الطلاب، و بعضهم يرى السبب في كثرة المفاهيم و المصطلحات وتعقيدها. تصنيف الأشياء يسهل على الطالب فهم الأمور خصوصاً في تلك المفاهيم المعقدة مثل مفاهيم المعالجات. لو تتبعنا المعالجات التي تنتجها الشركات و عرفنا خصائصها لوجدنا أنها فيها كثير من التطورات التي قد لا يدرسها الطالب إلا لو تعمق و تخصص في الإلكترونيات.

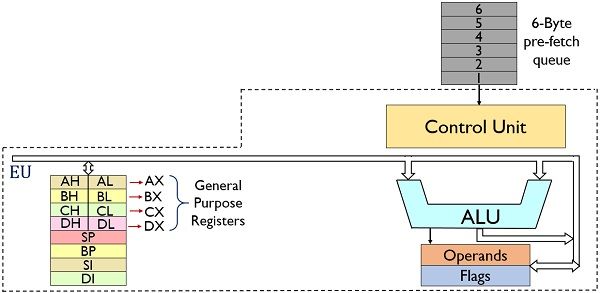

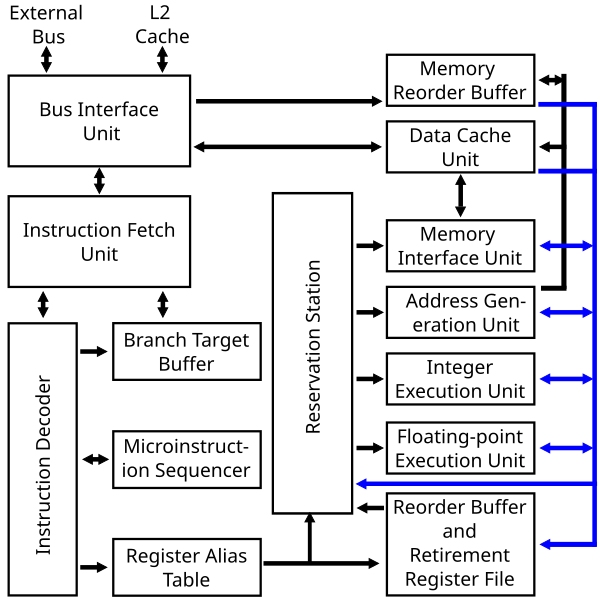

8086

تصنف معالجات x86 (التي تصنعها إنتل و AMD) أنها CISC، و يكثر الحديث أنها معالجات قديمة و لا تصلح. لو نظرنا لمعالجات x86 من إنتل و عرفنا تفاصيل أكثر، لعرفنا أن هذه الادعاءات أبعد ما تكون عن الصحة. مواصفات CISC التي تذكرها الكتب قد تصلح لفهم معالجات x86 القديمة، لكن ليست المعالجات الحديثة التي تنتجها إنتل أو AMD. معالج 8086 الذي منه بدأت معمارية x86 ذو خطوط متوازية pipelined و هذا قبل أن ظهور مفاهيم RISC التي سعت لتسهيل التوازي في دورة المعالج. معالج Pentium Pro ينفذ التعليمات حسب التنفيذ الحركي المرن dynamic execution و يسمى أيضاً التنفيذ مغاير الترتيب out-of-order execution، حيث يعيد المعالج ترتيب التعليمات حسب أولوية البيانات، و لهذا السبب يحتاج هذا النوع من المعالجات عدد كبير من المسجلات الفيزيائية physical registers أضعاف عدد مسجلات المعمارية architectural registers، و هذا موجود في المعالجات الحديثة (باستثناء معالجات المتحكمات الدقيقة microcontroller).

Pentium Pro

في الثمانينات كانت التوقعات أن معالجات x86 التي تنجها إنتل و غيرها ستنتهي، و سيحل محلها معالجات بمواصفات RISC. لم تصب تلك التوقعات التي توقعت نهاية عصر معالجات x86. بينما حدث العكس. لم تنتشر معالجات RISC كثيراً. عزا بعضهم السبب في أن إنتل تصنع بكثرة على عكس الشركات التي أنتجت معالجات بمواصفات RISC. لم أولد في تلك الفترة، لكن لا أظن أن هذا السبب منطقي.

قد تبدو فكرة التعليمات القليلة التي يسهل جعلها في خطوط متوازية رائعة نظرياً، لكن عملياً ليست كذلك. عانت معالجات RISC من مشكلة المعالج الخامل idle الذي يملأ وقت المعالج بفترات تأخير delay slots حتى يجلب التعليمات المتتابعة، ذلك لأن المعالج يستغرق الوقت في جلب التعليمات fetch أكثر من تنفيذ التعليمات execution. لم تسرع الخطوط المتوازية pipelines في أداء تلك المعالجات. تخلت الأجيال اللاحقة من معالجات RISC عن مبدأ التعليمات القليلة البسيطة، و بدأت بإضافة الكثير من التعليمات المعقدة و المتخصصة التي تنفذ في دورات متعددة. و هذا التغيير رأيناه في معالجات ARM الحديثة التي أضافت عملية القسمة في معالجاتها. بداية من معمارية ARMv8، أضافت ARM في كل مرة تعليمات جديدة للمعمارية، و لهذا برز لنا تسميات مثل ARMv8.1 و ARMv8.2، و انتقل هذا التحديث أيضاً لمعمارية ARMv9 و بالتالي ARMv9.1 و ARMv9.2 و غيرها من تحديثات على المعمارية. بعض هذه التعليمات مخصصة مثل تعليمات مخصصة لعمليات جافاسكريبت ( مثل تعليمة تحويل أعداد جافاسكريبت إلى أعداد صحيحة).

يربط كثيرون مفهوم RISC اليوم بالتعليمات ثابتة الطول fixed-length encoding، لكن حتى هذه الخاصية لم تلتزم بها المعالجات التي يقال أنها RISC. في معالجات ARM القديمة تعليمات Thumb، و هذه التعليمات ذات أطوال أقصر من تعليمات ARM و صنعت للعتاد الأدنى قوة، و استفاد منها جهاز GameBoy Advance حيث اعتمد برنامج BIOS الخاص بالجهاز على تعليمات Thumb. معالجات RISC-V (المعمارية التي بدأت تعليمية ثم صارت لها مواصفات لتستخدم في تطبيقات عملية) ذات تعليمات ثابتة الطوال للتعليمات الأساسية (التي لها فائدة أكاديمية فقط)، لكن تعليماتها متغيرة في حال الاعتماد على الامتدادات extensions ذات التعليمات متغيرة الطول، و هذا الموجود في معالجات RISC-V الصادرة لليوم. اضافت IBM في أحدث إصدار لمعماريتها PowerISA 3.1 خصائص من ضمنها التعليمات ذات السوابق prefixed instructions، و هذه التعليمات بطول 8 بايت، و هذا خلاف التعليمات الموجودة بطول 4 بايت. IBM نفسها لديها معمارية معالجات Z/Architecture التي صدر أول معالج منها سنة 2000، أي أنها ليست قديمة جداً، و هذه المعمارية خاصة بأجهزة الإطار الرئيس mainframe و التي هي خوادم لكن موجهة للاستخدام في البيانات الحساسة مثل البنوك، و تعليمات هذه المعمارية متغيرة الطول.

لو عرفنا تفاصيل المعالجات الحديثة، لوجدنا كثير من التعقيدات التي لا نجدها في المعالجات القديمة التي نراها في المعالجات قبل 40 سنة. هذه التعقيدات ليست عبثية بل وجدت لتطوير المعالجات أكثر و تحسين أدائها. الحديث عن معالجات بسيطة الهندسة خارج المتحكمات الدقيقة القديمة مضلل و غير صحيح. المشكلة في المحتوى المنتشر عن المعالجات الاعتماد على معلومات قديمة لا تصلح اليوم. المعالجات على أرض الواقع أكبر من أن تصنف في تصنيفات ثنائية أو ثلاثية أو أي تصنيفات تتجاهل تطورها و تغيرها.